Sviluppo: 1989–2000

Nel 1989, HP pensava che le architetture RISC (Reduced InstructionSet Computing) fossero bloccate ad un'istruzione per ciclo. I ricercatori HP cercarono di creare un nuovo tipo di architettura di processore, in seguito chiamato Explicitly Parallel Instruction Computing (EPIC), che permette al processore di utilizzare molte istruzioni in ogni ciclo di clock. EPIC utilizza una forma di architettura di istruzioni molto lunga (VLIW), in cui 1 parola di istruzione ha molte istruzioni. Con EPIC, il compilatore controlla quali istruzioni possono essere usate contemporaneamente, in modo che il processore possa eseguire le istruzioni senza bisogno di metodi complicati per vedere quali istruzioni usare contemporaneamente. L'obiettivo di questa idea è di permettere una migliore ispezione del codice al momento della compilazione per verificare la presenza di ulteriori opportunità per esecuzioni multiple in una sola volta, e di semplificare la progettazione del processore e risparmiare energia elettrica eliminando la necessità di istruzioni di programmazione del tempo di esecuzione.

HP pensava che non fosse un bene per le singole aziende di sistemi aziendali come HP realizzare processori proprietari, così HP ha collaborato con Intel nel 1994 per creare l'architettura IA-64, realizzata con le idee di EPIC. Intel voleva fare un grande sforzo nella creazione dell'IA-64 nell'aspettativa che il processore risultante sarebbe stato utilizzato dalla maggior parte dei sistemi aziendali. HP e Intel hanno avuto un grande sforzo di progettazione per realizzare il primo prodotto Itanium, Merced, nel 1998.

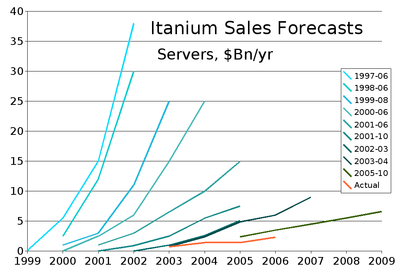

Durante la creazione, Intel, HP e altri analisti del settore hanno pensato che l'IA-64 sarebbe stato molto popolare nei server, nelle workstation e nei desktop e che un giorno avrebbe sostituito le architetture RISC e le complesse architetture CISC (Complex Instruction Set Computing) per applicazioni multiuso. Compaq e Silicon Graphics hanno smesso di lavorare sulle loro architetture Alpha e MIPS per passare all'architettura Itanium.

Molti gruppi hanno creato sistemi operativi per Itanium, tra cui Microsoft Windows, OpenVMS, Linux e tipi UNIX come HP-UX, Solaris, Tru64 UNIX e Monterey/64 (gli ultimi tre non hanno mai finito di lavorare con Itanium). Nel 1997, molti scoprirono che l'architettura Itanium e il compilatore erano più difficili da usare di quanto pensassero. Problemi tecnologici come gli altissimi conteggi dei transistor necessari per le grandi istruzioni e i grandi cache. [] Ci furono anche problemi con il progetto, in quanto le due parti del team usavano metodi diversi e avevano priorità leggermente diverse. [] Poiché Merced è stato il primo processore EPIC, la sua creazione ha avuto più problemi di quanto il team avesse pensato. Inoltre, il concetto EPIC richiedeva diverse capacità di compilazione che non erano mai state create prima, quindi era necessaria una maggiore ricerca. []

Intel ha annunciato il nome del processore, Itanium, il 4 ottobre 1999. In poche ore, il nome Itanic era stato usato per scherzo, (un riferimento al Titanic, la nave "inaffondabile" affondata nel 1912 ("Itanium + Titanic = Itanic"). "Itanic" è stato usato anche da The Register, e da altri, per dire che l'investimento multimiliardario in Itanium, e la domanda iniziale con esso, non avrebbe significato nulla perché pensavano che Itanium sarebbe fallita.

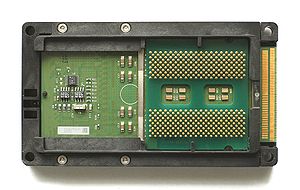

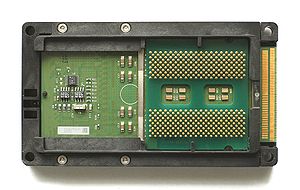

Itanium (Merced): 2001

| Itanium (Merced) |

|

|

| Prodotto | Da giugno 2001 a giugno 2002 |

| Produttore(i) comune(i) | |

| Max. Velocità di clock della CPU | 733 MHz a 800 MHz |

| Velocità FSB | 266 MT/s |

| Set di istruzioni | Itanium |

| Numero di nuclei | 1 |

| L2 cache | 96 KB |

| L3 cache | 2 o 4 MB |

| Presa(e) | |

| Nome(i) centrale(i) | |

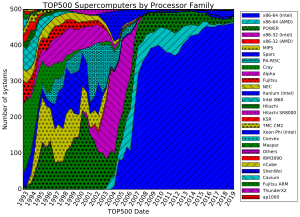

Al momento del rilascio di Itanium nel giugno 2001, le sue prestazioni non erano superiori a quelle dei processori RISC e CISC concorrenti. Itanium era in concorrenza con sistemi a bassa potenza (principalmente 4-CPU e piccoli sistemi) con server basati su processori x86, e con sistemi ad alta potenza come l'architettura POWER di IBM e l'architettura SPARC di Sun Microsystems. Intel ha spostato Itanium a lavorare con il business ad alta potenza e l'HPC computing, cercando di copiare il mercato di successo dell'x86 (cioè l'architettura 1, molti fornitori di sistemi). Il successo della prima versione del processore fu solo con la sostituzione di PA-RISC nei sistemi HP, Alpha nei sistemi Compaq e MIPS nei sistemi SGI, ma IBM realizzò anche un supercomputer basato su questa architettura. POWER e SPARC erano forti, e l'architettura x86 è cresciuta di più nello spazio aziendale, grazie ad una più facile scalabilità e ad una base di installazione molto grande.

Solo poche migliaia di sistemi che utilizzavano il primo processore Itanium, Merced, sono stati venduti, a causa delle scarse prestazioni, del costo elevato e del software meno itanium-made. Intel ha visto che Itanium richiedeva più software nativo per funzionare bene, così Intel ha realizzato migliaia di sistemi per i fornitori indipendenti di software per aiutarli a realizzare il software Itanium. HP e Intel portarono sul mercato il secondo processore Itanium, Itanium 2, un anno dopo.

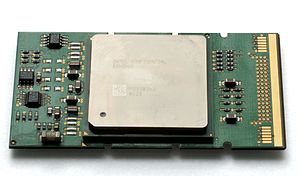

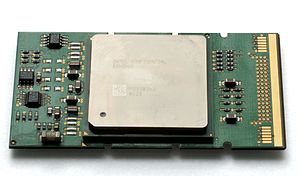

Itanium 2: 2002-2010

| Itanium 2 (McKinley) |

|

|

| Prodotto | Dal 2002 al 2010 |

| Creato da | Intel |

| Produttore(i) comune(i) | |

| Max. Velocità di clock della CPU | 900 MHz a 2,53 GHz |

| Set di istruzioni | Itanium |

| Numero di nuclei | 1, 2, 4 o 8 |

| L2 cache | 256 KB su Itanium2

256 KB (D) + 1 MB(I) o 512 KB (I) su (serie Itanium2 9x00) |

| L3 cache | 1,5-32 MB |

| Presa(e) | - PAC611

- FC-LGA6 (LGA1248) (serie Itanium 9300)

|

| Nome(i) centrale(i) | - McKinley

- Madison

- Hondo

- Deerfield

- Montecito

- Montvale

- Tukwila

- Poulson

|

Il processore Itanium 2 è stato rilasciato nel 2002, per i server aziendali e non per tutti i computer ad alta potenza. La prima versione di Itanium 2, denominata McKinley, è stata creata da HP e Intel. Ha risolto molti dei problemi del primo processore Itanium, che erano per lo più causati da un sottosistema di memoria difettosa. Il McKinley aveva 221 milioni di transistor (25 milioni dei quali erano per la logica), ed era 19,5 mm per 21,6 mm (421 mm2) ed è stato creato con un processo di progettazione a 180 nm, e un processo CMOS con 6 strati di alluminio.

Nel 2003, AMD ha rilasciato l'Opteron, che ha implementato la prima architettura x86-64 (all'epoca chiamata AMD64). Opteron ha avuto molto più successo perché è stato un facile aggiornamento da x86. Intel ha implementato x86-64 nei suoi processori Xeon nel 2004.

Intel ha rilasciato un nuovo processore Itanium 2, denominato in codice Madison, nel 2003. Madison ha utilizzato un processore da 130 nm ed è stata la base di tutti i nuovi processori Itanium fino al giugno 2006.

Nel marzo 2005, Intel ha annunciato che stava lavorando ad un nuovo processore Itanium, denominato in codice Tukwila, che sarà rilasciato nel 2007. Tukwila avrebbe avuto 4 core di processore e avrebbe sostituito il bus Itanium con una nuova Common System Interface, che sarebbe stata utilizzata anche da un nuovo processore Xeon. Più tardi in quell'anno, Intel ha cambiato la data di uscita di Tukwila alla fine del 2008.

Nel novembre 2005, i maggiori produttori di server Itanium hanno collaborato con Intel e molti fornitori di software per creare la Itanium Solutions Alliance, per promuovere l'architettura e accelerare il porting del software. L'Alleanza afferma che i suoi membri investiranno 10 miliardi di dollari in soluzioni Itanium entro la fine del decennio.

Nel 2006, Intel ha consegnato Montecito (commercializzato come la serie Itanium 2 9000), un processore 2 core che aveva circa 2x di prestazioni e il 20% in meno di consumo energetico.

Intel ha rilasciato la serie Itanium 2 9100, nome in codice Montvale, nel novembre 2007. Nel maggio 2009, il rilascio di Tukwila, il successore di Montvale, è stato nuovamente modificato, con il rilascio agli OEM previsto per il primo trimestre del 2010.

Itanium 9300 (Tukwila): 2010

Il processore della serie Itanium 9300, denominato in codice Tukwila, è stato rilasciato l'8 febbraio 2010, con prestazioni e quantità di memoria maggiori.

Tukwila utilizza un processo a 65 nm, ha tra due e quattro core, fino a 24 MB di cache della CPU, tecnologia Hyper-Threading e nuovi controller di memoria. Ha anche la correzione dei dati a doppio dispositivo, che aiuta a risolvere i problemi di memoria. Tukwila dispone anche di Intel QuickPath Interconnect (QPI) per sostituire l'architettura del bus Itanium. Ha una larghezza di banda massima del processore interno di 96 GB/s e una larghezza di banda massima della memoria di 34 GB/s. Con QuickPath, il processore ha controller di memoria integrati, che controlla la memoria utilizzando le interfacce QPI per comunicare con altri processori e hub I/O. QuickPath viene utilizzato anche con i processori Intel che utilizzano l'architettura Nehalem, in modo che Tukwila e Nehalem possano utilizzare gli stessi chipset. Tukwila incorpora quattro controller di memoria, ognuno dei quali supporta più DDR3 DIMM tramite un controller di memoria separato, simile al processore Nehalem Xeon denominato Beckton.

Itanium 9500 (Poulson): 2012

| | Questo articolo deve essere aggiornato. Puoi aiutare Wikipedia aggiornandolo. (Marzo 2014) |

Il processore della serie Itanium 9500, denominato in codice Poulson, è il processore successivo a Tukwila ed è stato rilasciato l'8 novembre 2012. Intel afferma di aver saltato la tecnologia di processore a 45 nm e di utilizzare invece la tecnologia di processore a 32 nm; è dotato di 8 core, ha un'architettura a 12 emissioni, integrazioni multi-threading e nuove istruzioni per il parallelismo, compresa la virtualizzazione. La dimensione della cache di Poulson L3 è di 32 MB. La dimensione della cache L2 è di 6 MB, 512 I KB, 256 D KB per core. La dimensione di Poulson è di 544 mm², meno della dimensione di Tukwila (698,75 mm²).

All'ISSCC 2011, Intel ha presentato un documento intitolato "A 32nm 3.1 Billion Transistor 12-Wide-Issue Itanium Processor 12-Wide-Issue Processor for Mission Critical Servers". Considerando la storia di Intel che ha condiviso i dettagli sui microprocessori Itanium all'ISSCC, questo documento si riferisce molto probabilmente a Poulson. L'analista David Kanter ipotizza che Poulson utilizzerà una nuova architettura, con una forma più avanzata di multi-threading che utilizza fino a due thread, per migliorare le prestazioni per il lavoro a singolo thread e multi-thread. Nuove informazioni sono state rilasciate alla conferenza Hot Chips.

Le nuove informazioni rivendicano miglioramenti nel multithreading, miglioramenti nell'affidabilità (Instruction Replay RAS) e alcune nuove istruzioni (priorità del thread, istruzioni intere, pre-fetching della cache, suggerimenti per l'accesso ai dati).

Nel documento Intel's Product Change Notification (PCN) 111456-01, sono elencati 4 modelli di CPU della serie Itanium 9500, che sono stati rimossi in una versione riveduta del documento. Le parti sono state successivamente elencate nel database MDDS (Material Declaration Data Sheets) di Intel. Intel ha successivamente pubblicato il manuale di riferimento Itanium 9500.

I modelli sono:

| Numero del processore | Frequenza |

| 9520 | 1,73 GHz |

| 9540 | 2,13 GHz |

| 9550 | 2,4 GHz |

| 9560 | 2,53 GHz |